物理结构

数据的存储方式

数据的大端和小端

- 小端方式:低位字节的地址小

- 大端方式:高位字节的地址小

32b半字地址是2的整数倍,字地址是4的整数倍,当所存数据不能满足此要求可以填充空白字节。这样保证对齐后,可以使得每次取数据都是一次性取出。

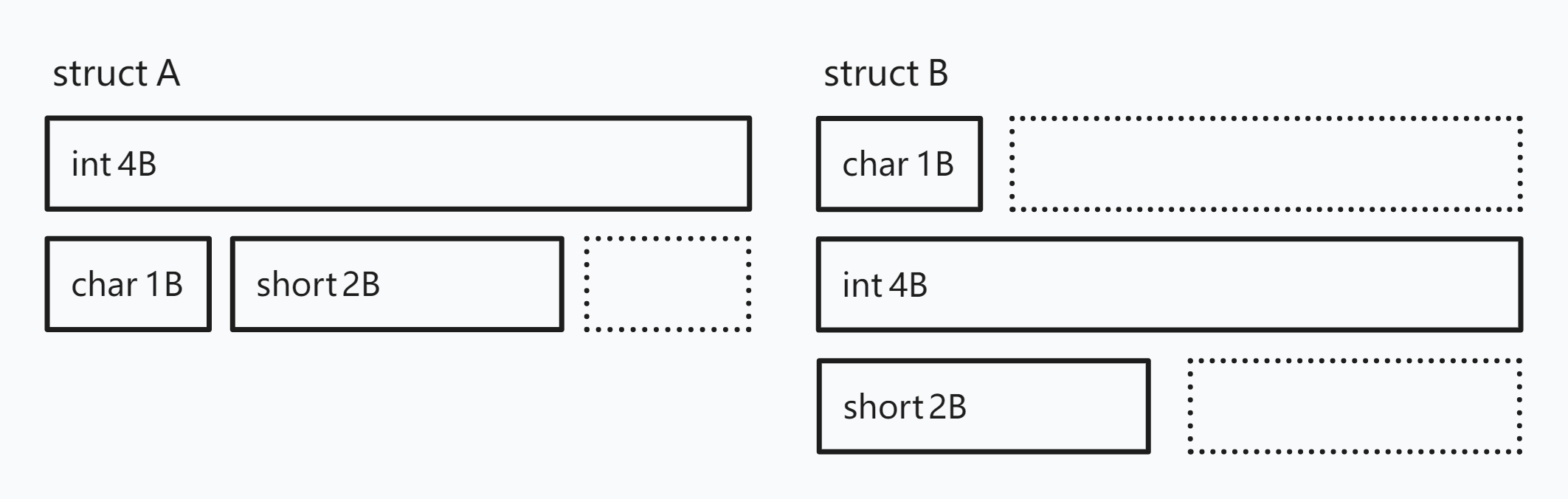

这里对比结构体存储:

sys32

struct A{

int a;

char b;

short c;

};

struct B{

char b;

int a;

short c;

};

//sizeof(A) = 8, sizeof(B) = 12

-

成员对齐地址:第一个成员在offset = 0的位置开始存储,后面的数据成员存储起始位置从该成员大小的整数倍开始存储。当数据成员是结构体时,成员大小按结构体中最大成员的大小计算。

-

收尾补齐:结构体的总大小是结构体内部最大成员的整数倍,不足要补齐。

存储器分类

| 类别 | 名称 | 说明 |

|---|---|---|

| RAM | DRAM | 主存 |

| SRAM | cache | |

| SDRAM | DDR | |

| ROM | MROM | 芯片生产过程中直接写入,任何人不能修改,用于工业控制机或电器 |

| PROM | 一次性编程的只读存储器,允许用户利用编程器进行一次写入,一旦写入,无法修改。 | |

| EPORM | 可以进行多次改写。编程次数有限,写入时间过长。 | |

| EEPROM | 电可擦除,IC卡 | |

| flash | U盘。可长期保存信息,也能在线快速擦除重写,且速度较快。 | |

| SSD | 基于闪存,用固态电子存储芯片阵列制成的硬盘,由控制单元和存储单元组成。闪存芯片代替传统的机械驱动器,闪存翻译器扮演磁盘控制器的角色。随机读很快,随机写很慢,且`SSD`会磨损。SSD分为若干块,每块`32-128page`分为若干页,读写单位是页(512B-4kB) | |

| 串行访问存储器 | DAM | 磁盘光盘 `CD-ROM` |

| SAM | 磁带 |

ROM和RAM都支持随机访问,但ROM一但有了信息,不轻易改变,掉电也不消失。两个显著优点:

- 结构简单,位密度比可读写存储器高;

- 具有非易失性。

相联存储器

相联存储器是按内容指定方式和地址指定方式结合进行寻址的存储器

- cache-MM-ES

- cache-MM 全透明

- MM-ES 半透明 只对应用程序员是透明的

DRAM芯片原理

地址码相同的多个存储元构成一个存储单元,若干存储单元的集合构成存储体。利用存储元电路上的栅极电容上的电荷来存储信息,基本存储元只使用一个晶体管,比SRAM的密度大,功耗低。相同地址的存储元件构成一个编址单位,可以按字、字节编址,现代计算机通常采用字节编址。

| 结构 | 说明 |

|---|---|

| 存储体(存储矩阵) | meta -> unit (same address)-> body |

| 地址译码器 | |

| IO控制电路 | |

CS控制信号 | 片选信号 |

WE控制信号 | 读写信号 |

刷新

电荷需要刷新,通常取2ms为刷新周期

- 集中刷新:一个刷新周期内用一段固定的时间,依此对存储器的所有行进行逐一再生。称为死时间,或访存死区。

- 分散刷新:分散到每个存取周期中

- 异步刷新:又充分利用最大刷新间隔为2ms的特点,具体操作为:在2ms内对128行各刷新一遍。即每隔15.6μs刷新一行(2000μs/128≈15.6μs),而每行刷新的时间仍为0.5μs。这样,刷新一行只能停止一个存取周期,但对每行来说,刷新间隔时间仍为2ms,而死时间为0.5μs。(相对每一段来说,是集中式刷新,相对整体来说,是分散式刷新)

读写周期

读写周期:行列地址分两次送。先送入读写信号WE,(读操作要当写数据在数据总线上保持稳定)行地址送到芯片地址引脚,行选通信号RAS,列地址送入芯片地址引脚,列选通信号CAS。控制总线(读写)指出总线周期的类型和本次输入、输出操作完成的时刻

地址引脚复用技术

行地址和列地址通过相同的引脚分先后两次输入,引脚数减少一半。

引脚:地址引脚+数据引脚+片段信号引脚1+读写信号2+(电源和接地线)

引脚复用后,片段信号搞成行选通和列选通2根

SRAM芯片原理

制造SRAM需要更多的硅。存储元是6晶体管MOS双稳态触发器,不需要再生,非破坏性读出。

行列地址一次送,默认两个读写线路,cache使用。